INTRODUCTION

High-speed machine vision systems find applications in many different industries. These hard real-time applications have demanding cycle-time and high-resolution image processing requirements. The cameras, which have a resolution of up to 8k pixels, deliver data streams of bandwidth up to 2 Gbps to be processed within a cycle time of 100 μs. A Machine Vision system that uses FPGA for interface and control, coupled with the acceleration offered by a GPU, is well suited to meet the high standard of requirements for such high-speed industrial applications.

MACHINE VISION SYSTEM ARCHITECTURE

Typically, any machine vision system has three stages: acquisition, processing and actuation. The acquisition stage involves handling high bandwidth transfer, trigger control, and if required, multi-camera synchronization. From there, the data is transferred to a vision processing module for image processing. And finally, the results of the processing are used to activate an actuator

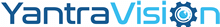

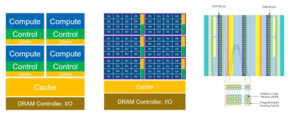

Most image processing pipelines are a series of operations performed on an image. To improve performance, the execution of both the pipeline and the operators can happen in parallel. However, the capacity of the system to perform parallel operations is dependent on the underlying hardware architecture. The CPU, GPU, and FPGA architectures offer varying degrees of capability in multiple dimensions like programmability, complexity, flexibility etc. which must be leveraged properly for optimized performance depending on the application.

FPGA FOR HIGH-SPEED INTERFACE IN MACHINE VISION

An FPGA consists of numerous internal hardware blocks, called configurable logic blocks (CLB), with user-programmable interconnects that can be reconfigured any number of times; this gives the FPGA a high degree of flexibility and parallel processing ability. FPGA can interface with other devices via either the I/O ports located on its periphery or via a serial transceiver, The I/O ports can be configured to connect to proprietary interfaces and are generally used to connect the FPGA to the camera or the actuator. The serial transceiver is used for high-bandwidth interfaces in the order of Gbps since it takes care of signal integrity without any noise or skew. These capabilities make FPGA very consistent and capable of handling high bandwidth interfaces and pixel-level image processing operations like color space conversion, thresholding etc.

GPU ACCELERATION FOR MACHINE VISION APPLICATIONS

The GPU is best suited for algorithms involved in image-level processing that require access to large memory. High-end GPUs from NVIDIA can have as many as 3000+ cores, with each being able to execute multiple computations in parallel. Many of these image-level processes require matrix multiplication of floating points values, and GPU architecture is very efficient for these operations. For example, many of the filters used in operations like Edge detection use convolution, which are accelerated effectively using GPU. Moreover, GPU is very effective for Deep Learning inference.

YANTRAVISION AS SYSTEM DESIGN PARTNER

The challenge in working with FPGAs and GPUs is that exploiting their full capabilities requires a high degree of skill and knowledge in hardware and software engineering. At YantraVision, we have the experience and the expertise to do so. We have developed FPGA based IPs and GPU accelerated algorithms for a diverse range of applications, from high-speed print inspection to free fall sorting.